图像线性插值Verilog代码,已通过FPGA验证(Image linear interpolation Verilog code, has been verified by FPGA)

”fpga开发 verilog 图像线性插值“ 的搜索结果

1.例程具有说明文件; 2.例程具有仿真文件; 3.例程使用FPGA实现了二次线性插值算法。

此为可编译通过的工程文件

FPGA图像处理5-基础功能-双线性插值(原理) fpga开发.pdf

双线性插值算法的FPGA实现,Verilog代码,分享给大家一起学习!

2.内容:quartusii平台通过verilog编程实现bilinear双线性插值,将100x100图像进行插值处理 3.用处:用于bilinear双线性插值算法编程学习 4.指向人群:本科,硕士,博士等教研使用 5.运行注意事项: 工程路径...

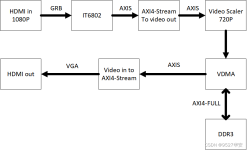

紫光同创FPGA纯verilog代码实现图像缩放,两种插值算法任意尺寸缩放,提供3套PDS工程源码 本设计提供3套Pango Design Suite 2021.4版本的工程源码,工程1默认采集OV7725摄像头,输入分辨率为640x480@60Hz,经过图像...

国产高云FPGA:纯verilog实现视频图像缩放,提供6套GOWIN工程源码和技术支持 本文使用国产高云GW2A-LV18PG484C7/I6型号的FPGA做纯verilog实现视频图像缩放,视频源有两种,分别对应开发者手里有没有摄像头的情况,一...

本文主要讨论了如何在FPGA上实现双线性插值的计算。Interp和Resize是Yolo_v2,Yolo_v3和Faster R-CNN等目标检测网络的关键层。主要的作用是使得图片的放大和缩小过程变得更为平滑。

FPGA高端项目:Xilinx Zynq7020 系列FPGA纯verilog图像缩放工程解决方案 提供3套工程源码和技术支持

开发环境: IDE:LIBERO 9.0(ACTEL公司的) 芯片:AFS600 (BGA256),是混合系列的FPGA ...参考大学写的一段图像插值的C程序写的,先看看这个简单的插值C函数,水平很烂,别见笑: YBYTE

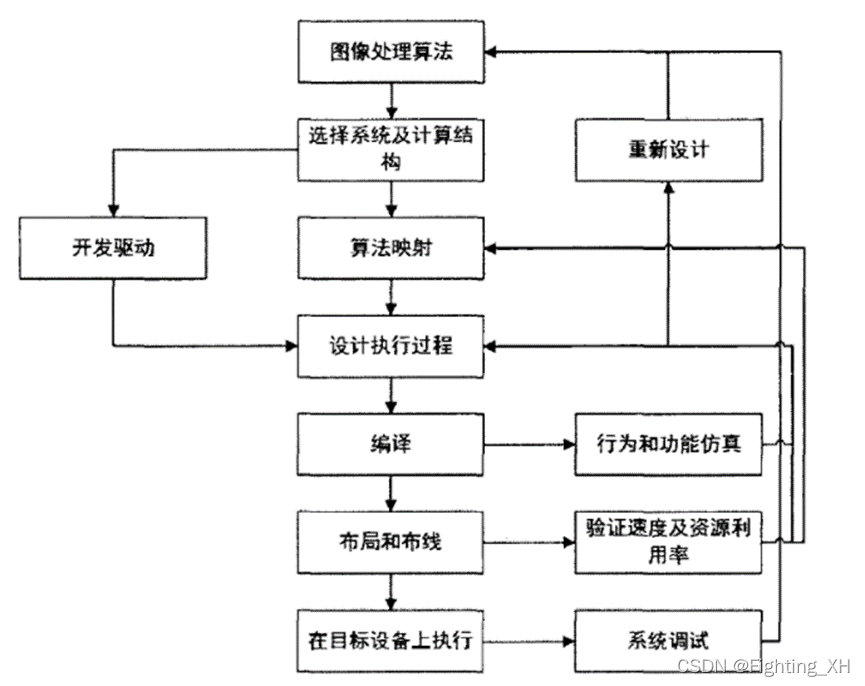

FPGA图像处理基础 一、简述 图像处理(image processing),用计算机对图像进行分析,以达到所需结果的技术。又称影像处理。图像处理一般指数字图像处理。数字图像是指用工业相机、摄像机、扫描仪等设备经过拍摄得到的...

直方图均衡 直方图均衡算法通过将各颜色通道的像素点数值间距拉大...对于 RGB 图像,可以先将其转化为 YUV 图像,仅对 Y 通道执行直方图均衡算法后,再由 YUV 图像转化为 RGB 图像,实现彩色图像的增强。 一般情况...

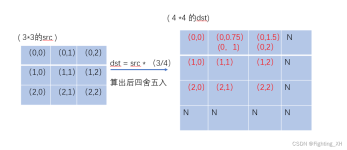

双线性插值算法是一种图像处理算法,可以用于图像的放大或缩小操作。在Verilog中,可以通过编写相应的模块来实现双线性插值算法。 双线性插值算法的原理是在待处理图像的相邻四个像素点之间进行插值计算,从而得到...

使用插值算法实现图像缩放是数字图像处理算法中经常...在图像的缩放处理过程中,经常会用到插值算法,常见的插值算法包括最邻近插值,双线性插值,双三次线性插值,兰索斯插值等方法。其中,双线性插值由于折中的...

FPGA高端项目:FPGA基于GS2971的SDI视频接收+纯verilog图像缩放+多路视频拼接,提供8套工程源码和技术支持

FPGA高端项目:FPGA实现SDI视频编解码+图像缩放 工程解决方案,提供3套工程源码和技术支持

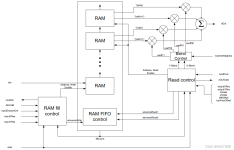

在FPGA实现算法,比较复杂。结果验证和 FPGA自带的效果差不多。占的资源比较少。 双线性插值的框架图: 双线性插值的运算单元: 这样就可以实现视频的缩放。

推荐文章

- cocos creator 实现截屏截图切割转成 base64分享--facebook小游戏截图base64分享,微信小游戏截图分享【白玉无冰】每天进步一点点_cocos上传base64-程序员宅基地

- Docker_error running 'docker: compose deployment': server-程序员宅基地

- ChannelSftp下载目录下所有或指定文件、ChannelSftp获取某目录下所有文件名称、InputStream转File_channelsftp.lsentry获取文件全路径-程序员宅基地

- Hbase ERROR: Can‘t get master address from ZooKeeper; znode data == null 解决方案_error: can't get master address from zookeeper; zn-程序员宅基地

- KMP的最小循环节_kmp求最小循环节-程序员宅基地

- 详解ROI-Pooling与ROI-Align_roi pooling和roi align-程序员宅基地

- Imx6ull开发板Linux常用查看系统信息指令_armv7 processor rev 2 (v7l)-程序员宅基地

- java SSH面试资料-程序员宅基地

- ant design vue table 高度自适应_对比1万2千个Vue.js开源项目发现最实用的 TOP45!火速拿来用!...-程序员宅基地

- 程序员需要知道的缩写和专业名词-程序员宅基地